Code No: 153AT

**R18**

## JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD B. Tech II Year I Semester Examinations, March - 2022 ELECTRONIC DEVICES AND CIRCUITS

(Common to ECE, EIE, MCT)

Time: 3 Hours

Max. Marks: 75

Answer any five questions

All questions carry equal marks

1.a) With a neat circuit diagram, Explain the operation of Full Wave Rectifier with Capacitor filter.

b) A Half Wave Rectifier circuit supplies 100 mA DC current to a 250 Ω load. Find the DC output voltage, PIV rating of the diode and rms voltage for the transformer supplying the rectifier.

[9+6]

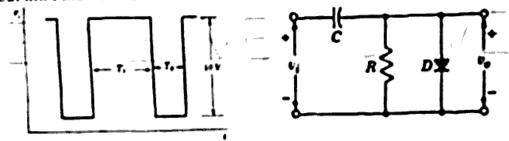

State and prove Clamping Circuit Theorem.

b) An unsymmetrical square wave with T<sub>1</sub> = 1 msec and T<sub>2</sub> = 1 µsec has an amplitude of 10 V. This signal is applied to the restorer circuit of figure 1, in which R<sub>f</sub> = 50Ω, R = 50 KΩ. Assume that the capacitor C is arbitrarily large, so that the output is a square wave without tilt. Find where, on the waveform, the zero level is located. [8+7]

Figure: 1

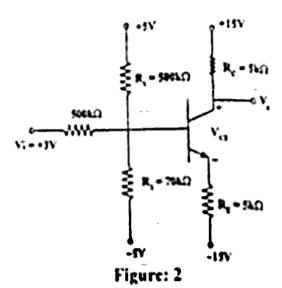

3.a) Draw and explain the input and output characteristics of BJT in CE configuration.

b) In the circuit shown in figure 2, with β = 100. Determine I<sub>CO</sub>, V<sub>CO</sub> and draw the DC load line. [8+7]

- Explain the working of the transistor as a switch. 4.a)

- In a silicon transistor with a fixed bias,  $V_{CC} = 9 \text{ V}$ ,  $R_C = 3 \text{ k}\Omega$ ,  $R_B = 8 \text{ k}\Omega$ ,  $\beta = 50$ . b)  $V_{BE} = 0.7 \text{ V}$ . Find the operating point and stability factor S. 17+81

- Illustrate the construction and principle of operation of JFET with necessary diagrams, 5 5.a)

- A FET follows the relation  $I_D = I_{DN} \left[1 \frac{V_{ef}}{V_e}\right]^2$ . What are the values of  $I_D$  and  $g_{ef}$  for b) V<sub>Gy</sub>=-1.5 V if I<sub>GS</sub> and V<sub>P</sub> are given as 8.4 mA and -3 V respectively?

- 17+4+41 State any three differences between JFET and BJT. Any c)

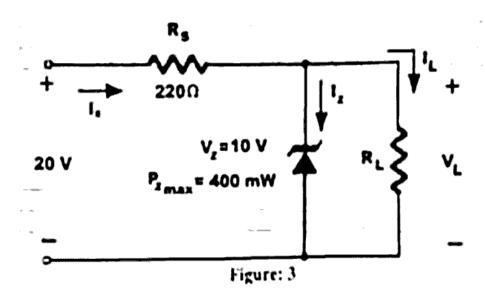

- Explain the construction of SCR with neat diagram. Draw its V-I characteristics. 6.a)

- Determine the value of R<sub>1</sub> that will establish maximum power conditions for the zener b) 18 + 71diode shown is circuit shown in figure 3.

- Draw the h-parameter equivalent circuit for a typical common base amplifier and derive 7.a) expression for A., A., R. and R., https://www.jntuonline.com

- In the CE amplifier calculate the mid frequency voltage gain and lower 3-dB point. The b) transistor has h-parameters  $h_{te} = 400$  and  $h_{ee} = 10 \text{ k}\Omega$ , the circuit details are  $R_{\bullet} = 600 \Omega$ .  $R_1 = 5 \text{ k}\Omega$ ,  $R_s = 1 \text{ k}\Omega$ ,  $V_{cc} = 12 \text{ V}$ ,  $R_1 = 15 \text{k}\Omega$ ,  $R_2 = 2.2 \text{ k}\Omega$  and  $C_c = 50 \mu\text{F}$ . 18-71

- Draw the transfer and drain characteristics of MOSFET and explain the three regions of \* 8.a) operation of a MOSFET

- Derive an expression for voltage gain, input impedance and output impedance of CG b) amplifier at low frequencies. [7+8]